第 6 章 存储器

一. 概述

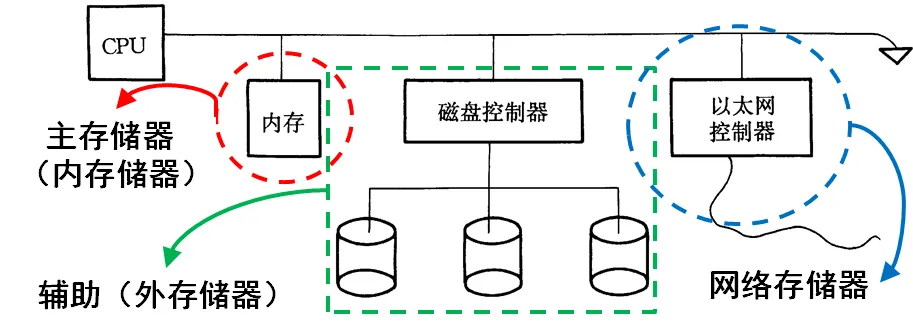

为了使容量、速度与成本适当折中,现代计算机系统都是采用多级存储体系结构:主存储器(内存储器)、辅助(外)存储器以及网络存储器。

1. 总体分类

1.1. 内存

- 主内存

- 高速缓冲存储器 Cache

1.2. 外存

- 联机外存

- 脱机外存

2. 存储器系统

将两个或两个以上速度、容量和价格各不相同的存储器用硬件、软件或软硬件相结合的方法连接起来。

使整个系统的存储速度接近最快的存储器,容量接近最大的存储器,价格接近最便宜的存储器。

2.1. Cache 存储系统

- 高速缓冲存储器(Cache)和主内存构成,由硬件系统负责管理。

- 对程序员透明:对原本存在的事物,从某个角度看上去不存在。

- 提高 CPU 访问内存的存储速度

2.2. 虚拟存储系统

- 由主内存和部分硬磁盘构成,主要由操作系统管理。

- 解决主存容量不足的问题,使得编写程序时不用考虑主存大小:部分硬磁盘的空间可以作为主存使用。

- 扩大存储容量

二. 半导体存储器的分类

1. 定义

- 由能够表示二进制数 0 和 1 的,具有记忆功能的半导体器件组成

- 能存放一位二进制数的半导体器件称为一个存储元

- 每个存储单元需要 8 个存储元构成

分类树

- 半导体存储器

- 读写存储器 RAM

- 双极型

- MOS

- 静态

- 动态

- 只读存储器 ROM

- 掩模 ROM

- 可编程 ROM(PROM)

- 可擦去的 ROM(EPROM)

- 读写存储器 RAM

2. 读写存储器 RAM(随机存取存储器)

主要用来存放各种现场的输入输出数据,中间计算结果,与外村交换的信息和堆栈作用。

2.1. 双极型 RAM 特点

- 存取速度高。

- 以晶体管的触发器(F-F——Flip-Flop)作为基本存储电路,故管子较多。

- 集成度较低(与 MOS 相比)。

- 功耗大。

- 成本高。

双极型 RAM 主要用在对速度要求较高的微型机中或作为 Cache。

2.2. MOS RAM

2.2.1. 静态 RAM(SRAM)

- 6 管构成的触发器作为基本存储电路。

- 集成度高于双极型,但低于动态 RAM。

- 不需要刷新,故可省去刷新电路。

- 功耗比双极型的低,但比动态 RAM 高。

- 易于用电池作为后备电源。

- 存取速度较动态 RAM 快。

2.2.2. 动态 RAM(DRAM)

- 基本存储电路用单管线路组成(靠电容存储电荷)。

- 集成度高。

- 比静态 RAM 的功耗更低。

- 价格比静态便宜。

- 动态存储器靠电容来存储信息,由于存在着泄漏电流,故需要定时刷新。典型的是要求每隔 1ms 刷新一遍。

3. 只读存储器 ROM

用来存放固定的程序,如微型机的管理、监控程序,汇编程序,存放各种常数、函数表等。

- ROM 电路比 RAM 简单,集成度更高,成本更低;

- ROM 在电源去掉之后不会丢失信息,因此计算机经常将一些管理和监控程序、操作系统的基本输入输出程序(BIOS)以及各种典型的程序放在 ROM 中。

3.1. 掩模 ROM

- 按照固定线路制造,出厂时已经制作好数据,只能读不能改变;

- 适用于批量生产的产品,成本较低,不适用于研究工作。

3.2. 可编程序的只读存储器 PROM(Programmable ROM)

- 用户可对 PROM 进行编程;

- PROM 只能写入一次。

3.3. 可擦去的可编程只读存储器 EPROM(Erasable PROM)

- EPROM 能够根据需求写入信息,能够将写入的信息擦掉,内容可以改写多次;

- EPROM 的写入速度较慢并需要一些额外条件,使用时仍作为只读存储器使用。

半导体存储器的主要技术指标

- 存储容量 = 存储单元数 × 每单元的二进制数

- 存取时间 = 实现一次读/写所需要的时间

- 存取周期 = 连续启动两次独立的存储器操作所需间隔的最小时间

- 可靠性、功耗

三. 读写存储器 RAM

1. 基本存储电路

组成存储器的基础和核心,分为 SRAM 和 DRAM

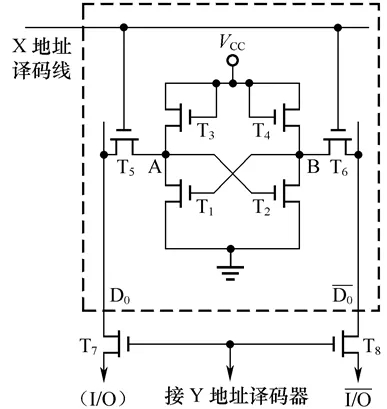

1.1. 六管 SRAM

静态存储电路是由两个增强型的 NMOS 反相器交叉耦合而成的触发器。

将触发器作为存储电路需要控制能否被选中,形成下图所示的 6 管的基本存储电路。

- 为控制管

- 为负载管

- 当 的译码输出线为高电平, 导通, 端与位线 相连

- 当 的译码输出线为高电平, 导通, 与输入输出电路 相通

- 只要电源不掉电,就能保持信号

Example

-

- 导通, 截止,相当于把输入电荷存储于 管的栅极

- 地址线为高电平时, 与 相通, 与 相通

- 读出时将 和 线连接到一个差动放大器,由其电流方向判定存储单元的信息是“1”还是“0”;

- 也可以只有一个输出端接到外部,以其有无电流通过而判定所存储的信息。

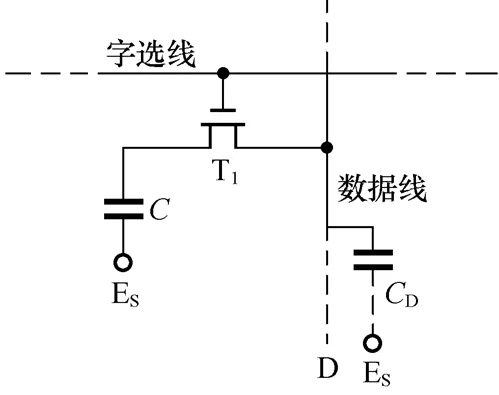

1.2. 单管存储电路

1.2.1. 写入

- 字选线为高电平, 管导通,信号由数据线存入电容 C

1.2.2. 读出

- 字选线为高电平, 管导通,存储在电容 C 上的电荷通过 输出到数据线上

- 每次读出数据后,存储内容会被破坏(电容放电),如需保存原信息必须采取恢复措施

- 电容会漏电,需要定期刷新

1+. 存储单元的编址

地址线

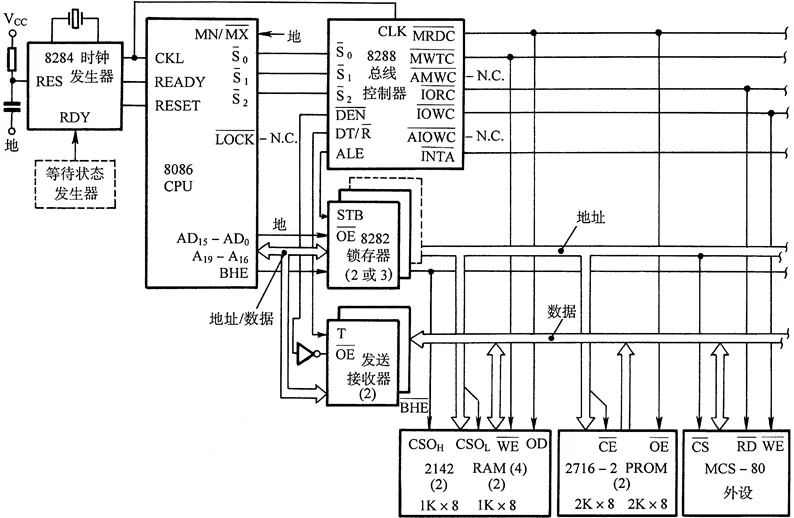

以 8086 为例,由于单片 8086 的性能有限,在实际工作时是需要其他的部件进行配合的。

- 以 8086 的 20 位地址信号通过地址锁存器与地址总线连接。

- 20 位地址信号用来确定某一个要访问的内存单元的地址。

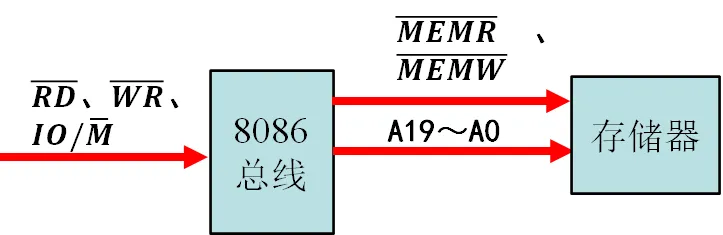

为低电平,进行存储器访问

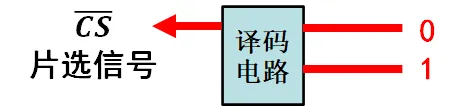

译码电路

- 将输入的一组高位地址信号通过变换,产生一个有效的输出信号(片选信号 ),用于选中某一个存储器芯片,从而确定了该存储器芯片在内存中的地址范围。

编址

任何一个存储单元在存储空间中都有唯一的地址,即如果假设对应的存储单元在某一芯片上,这个存储单元一定要有一个完整存储空间的地址。

| 高位地址 | -低-位-地-址- |

|---|---|

| 片选地址 | -片-内-地-址- |

| 片选:地址 | 存储单元 | 片选:地址 | 存储单元 | 片选:地址 | 存储单元 |

|---|---|---|---|---|---|

00:00 | XX | 01:00 | XX | 10:00 | XX |

00:01 | XX | 01:01 | XX | 10:01 | XX |

00:10 | XX | 01:10 | XX | 10:10 | XX |

00:11 | XX | 01:11 | XX | 10:11 | XX |

2. RAM 的结构

- 一个基本存储电路表示一个二进制位,因而存储器是由大量的存储电路组成的。存储电路有规则地组合起来就是存储体;

- 为了区别不同的存储单元,需要对存储单元进行编号,即地址;

- 电路通过地址寄存器和地址译码器以及驱动电路选择对应单元,通过放大器将信息放大读出信息。总之,存储器中除了存储体外还需要相应的外围电路。

- 较大容量的存取器中,往往将各个字的同一位组织在一个片中。

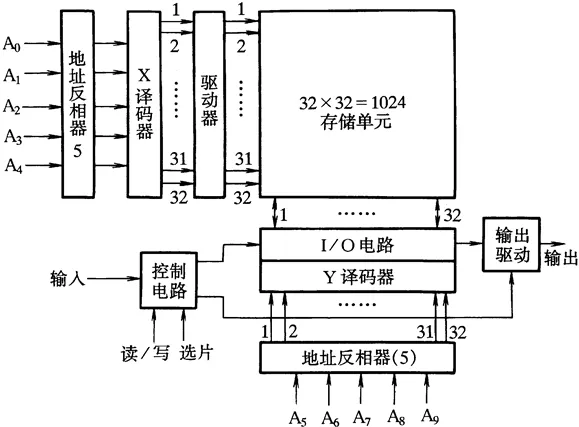

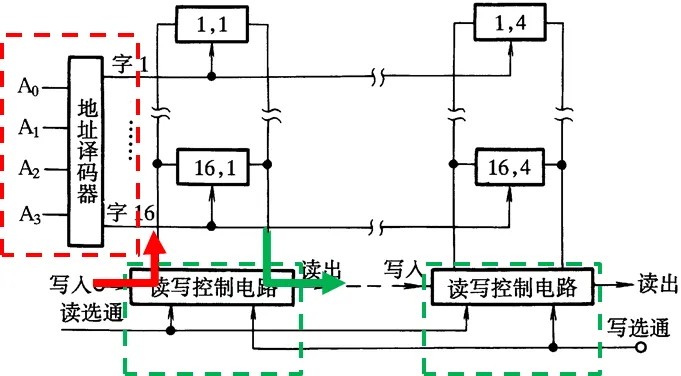

2.1. 典型 RAM 示意

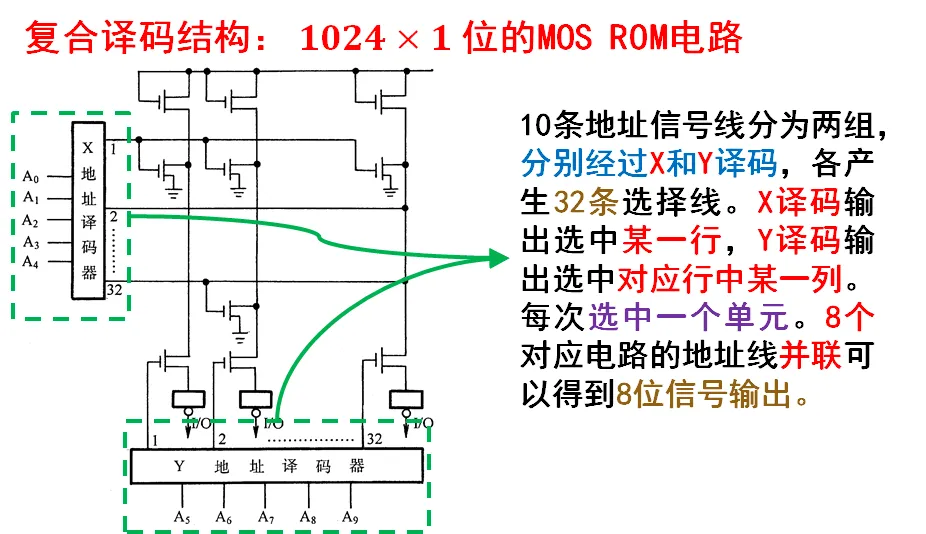

- 1024 个字的同一位按照矩阵形式排列,32 × 32 = 1024

- 地址译码器确定存储单元和所在行和列,最终找到存储单元

2.2. 存储器外围电路

- 地址译码器

- 存储器对 CPU 发出的地址信号进行译码用以选择需要访问的存储单元

- I/O 电路

- 位于数据总线和被选用的存储单元之间,用以控制被选中单元的读写,并具有放大信息的作用

- 片选控制端(CS, Chip Select)

- 由于单片芯片的存储容量优先,所以一个存储体由多个芯片组成。因此,在地址选择时需要先进行选片,用地址译码器输出和一些控制信号形成片选信号。只有 CS 有效选中某一片时,此片所连的地址线才有效,进而可以对选中芯片上的存储单元进行读写操作

- 集电极开路或三态缓冲器

- 通过集电极开路可以实现多片 RAM 数据线的并联使用,扩展存储器指数。通过三态输出缓冲器实现存储体与双向数据总线的连接

2.3. 地址译码的方式

2.3.1. 单译码结构

- 单译码结构适用于小容量存储器,存储器==线性==排列,以字选择线来选择某个字的所有位,特点是地址译码器输出线较多;

- 当地址译码器有 根输入线时,其对应的输出线为 根。

- 图中,地址信号 0100 选择第 5 条字线的所有位

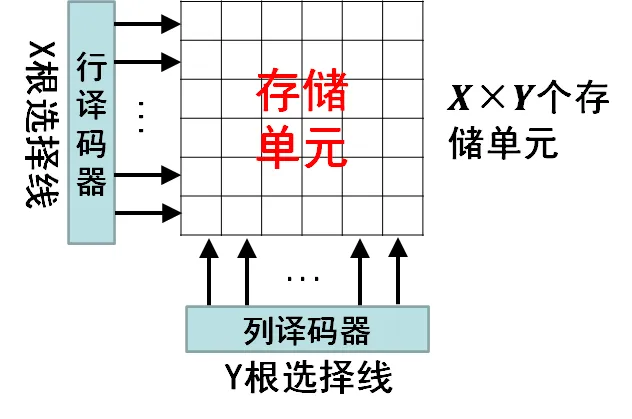

2.3.2. 双译码结构

- 存储器以矩阵的形式排列,将地址线分为两部分,对应的译码器也是两部分,即行译码器和列译码器;

- 行译码器输出行地址选择信号,列译码器输出列地址选择信号,行列选择选择线交叉处即为选中的内存单元;

- 一共可以表示个存储单元

例题

若需要 1024 个输出状态,在双译码结构的条件下, 和 地址译码器的输入端数目一致,那么单个译码器的输入端有多少?这种情况下两个译码器需要多少选择线?

- 若 ,双译码的输出状态为 个,那么单个译码器的输入端需要 5 个。

- 两个译码器的选择线=单个译码器的选择线

单个译码器支持 1024 个输出状态需要 1024 根选择线

双译码结构译码输出线较少,适用于较大的存储器系统。

- 10 根地址线

- 输出至 译码器输出 条选择线,分别选择 行

- 输出至 译码器输出 条选择线,分别选择 列

- 输入地址 00100 00010

- 方向选中 00100,对应第 5 行

- 方向选中 00010,对应第 3 列

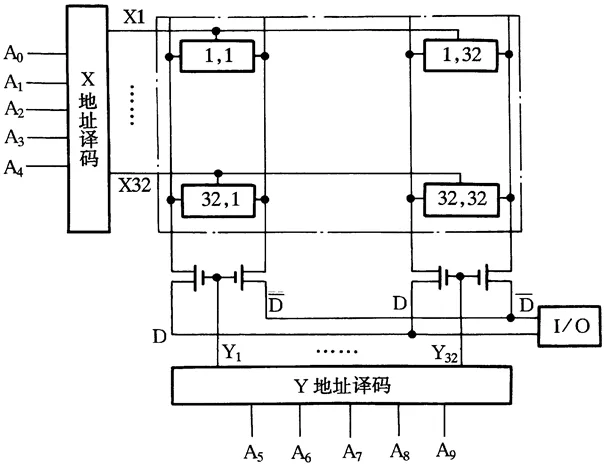

2.4. 静态 RAM 实例 Intel 2114

- 地址线

- 片选信号

- 写允许

- 数据输入输出

1K × 4 位芯片,需要 1024 个地址(10 根地址线),每个地址对应 4 位数据。设计为 64 × 16 的结构。

- 行译码

- 列译码

- 有效时,通过 进行写入/读出控制

- 低电平:输出三态门导通,信号由数据总线写入

- 高电平:输出三态门打开,从存储器读出信号送至数据总线

3. RAM 与 CPU 的连接

3.1. 连接

CPU 对存储器进行读写操作,首先要由地址总线给出地址信号,然后要发出读/写的控制信号,最后在数据总线上进行信息交流。所以,RAM 与 CPU 的连接,主要有以下三个部分:

- 地址线的连接

- 数据线的连接

- 控制线的连接

3.2. 需考虑的问题

3.2.1. CPU 的负载能力

- 小型系统中,CPU 直接与存储器相连

- 大型系统中,需要考虑 CPU 是否能带动,需要时加上缓冲器,由缓冲器的输出再带来负载

3.2.2. CPU 的时序和存储器的存取速度之间的配合问题

- CPU 在取指和存储器读或写操作时,是有固定时序的,因此对存储器的存取速度有要求。在存储器确定的情况下,需要考虑是否需要 周期,以及如何实现。

3.2.3. 存储器的地址分配和选片问题

- 内存通常分为 RAM 和 ROM,RAM 又分为:系统区、用户区(数据区和程序区)→ 内存的地址分配;

- 单片存储器容量有限,需要多片共同组成一个存储器 → 产生片选信号进行选片。

3.2.4. 控制信号的连接

- CPU 发出的控制信号 与存储器要求的控制信号相连。

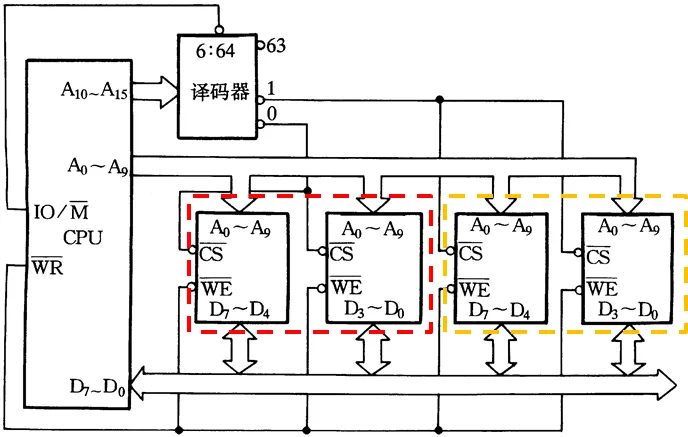

3.3. 例子

用 Intel 2114 来构成一个 2KB RAM,需要 片 2114 芯片,两片一组,每组为一个 1KB × 8 位的 RAM

- 数据信号

- 每片 RAM 的地址线 直接与 CPU 的地址总线 相连接,可寻址 1KB

- 经过译码后可以产生 64 条选择线以控制不同的组,系统共为 2KB,RAM 可以分为两组,通过片选信号进行区分

- 控制信号

- 连接译码器控制译码器工作

- 连接

| 高位地址 | 地位地址 |

|---|---|

| 0000000000 | |

| 1111111111 |

3.4. 译码方式

3.4.1. 全地址译码

将全部的高位地址信号作为译码信号,使得存储器芯片的每一个单元都占据一个唯一的内存地址。

- 不浪费地址资源

- 线路设计相对复杂

例

实例系统为 2KB,只需要两条选择线,比如使用地址最低的两条,即 000000 和 000001,两组存储器的地址分配为:

| 第一组 | ||

|---|---|---|

| 地址最低 | 000000 | 0000000000 |

| 地址最高 | 000000 | 1111111111 |

即为:0000~03FFH

| 第二组 | ||

|---|---|---|

| 地址最低 | 000001 | 0000000000 |

| 地址最高 | 000001 | 1111111111 |

即为:0400~07FFH

3.4.2. 部分地址译码

将部分的高位地址信号作为译码信号,被选中的存储芯片占有几组不同的地址范围。

- 减少了控制线的数量

- 浪费了地址资源

例题

部分译码方式下对 Intel 2114 进行选片控制,如果采用 和 控制选片,那么可以控制几片 Intel 2114 芯片,这种情况下被选中的芯片在内存中的重叠区域有多大?

- 可以控制 片

- 被选中芯片内存重叠区域为

- 和 用于片选,其他线进行地址分配

3.4.3. 线选方式

- 将 CPU 的地址线直接与芯片的 相连

- 结构简单,不需要译码电路

三. 只读存储器

1. 掩模 ROM

由二极管,双极型晶体管或 MOS 电路构成,这类 ROM 工作原理是类似的。掩模 ROM 在制造时就已经将数据从电路上写好,无法修改。

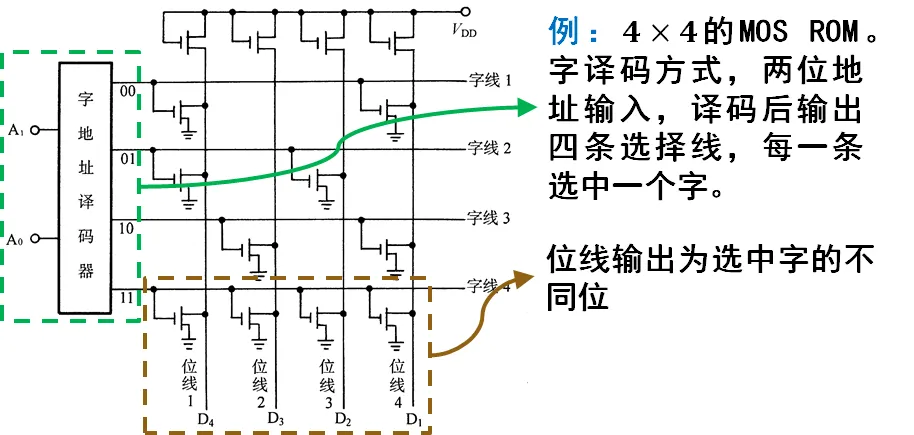

1.1. 字译码结构

采用字译码方式,字地址译码器,输出选择线,每一条选中一个字,位线输出即为这个字的各位。

地址信号 00 选中第一条字线,输出高电平。与位线 1、位线 4 相连的 MOS 管到店,位线输出为 0;位线 2 与位线 3 无 MOS 管相连,输出为 1。实际输出到总线上是 1 还是 0,取决于输出线上是否有反相。

1.2. 复合译码结构

地址信号线分为两组,分别进行 和 译码,选中对应单元。

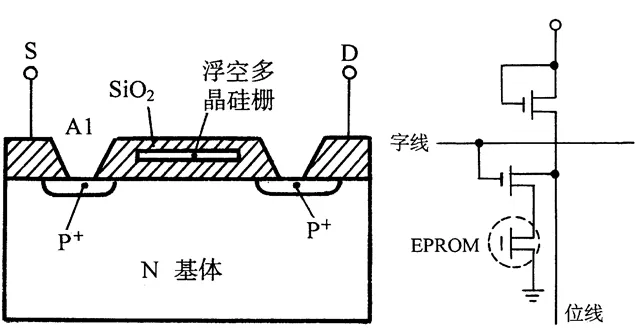

2. EPROM

2.1. 基本存储电路

- D、S 之间绝缘物 包裹多晶硅栅极,初始状态硅栅上没有电荷,D、S 之间不导电。

- EPROM 管用于存储矩阵时的基本电路。

- 写入时在 D、S 两极之间加上 25V 的高压,D、S 之间被击穿,电子注入硅栅。去除高压后,硅栅上电子无法漏走,形成导电沟道使 EPROM 导通输出为“0”(或“1”)

2.2. 功能

- EPROM 存储电路做出的芯片上方有一个石英玻璃的窗口,用紫外线通过窗口照射时,所有电路中的浮空晶栅上的电荷会将光电流泄漏走,电路恢复起始状态,将写入的信号擦去;

- 照射之后的 EPROM 可以实现重写。由于写入过程很慢,因此 EPROM 一般作为只读存储器使用。

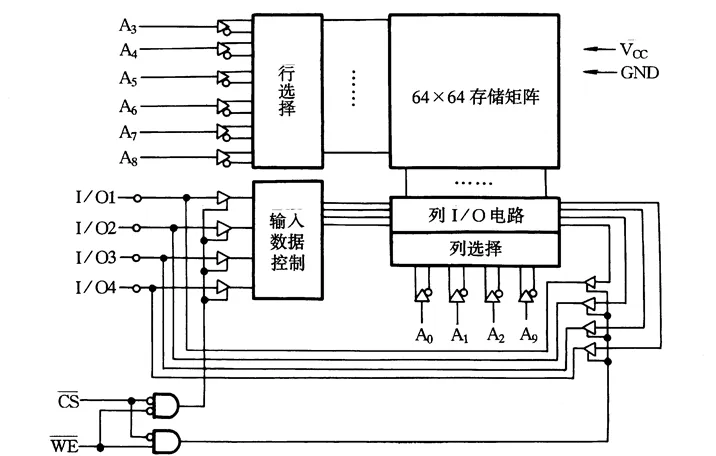

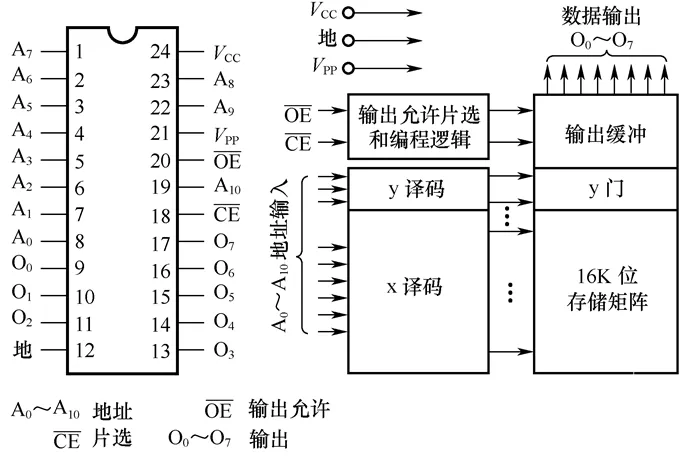

2.3. 实例 Intel 2716 (2K × 8 bit)

- : 共 11 条地址线

- : 共 8 位数据输出,8 位输出均有缓冲器

- 译码 : 7 条地址线用于 译码,用以选择 128 行中的一行,4 条地址线用作 译码

- : 片选

- : 输出允许

Intel 2716 的编程写入

- 2716 在出厂时或在擦除后,所有单位的内容全为“1”,要使某一位为“0”必须通过编程;

- 编程需要逐单元的进行;编程时 接至 +25V, 接高电平,写入数据接至 2716 的数据输出线;

- 地址和数据稳定之后在 输入端加上一个 50ms 的正脉冲,在正脉冲的作用下,可以使内部的管子瞬时击穿,浮空栅截获足够数量的电子。脉冲过后管子恢复,相当于给浮空栅加上负电源,管子导通,存储内容变为“0”。

- 使用时需要避免阳光照射以免电荷泄漏,芯片的照射窗口需要贴上黑色保护层。

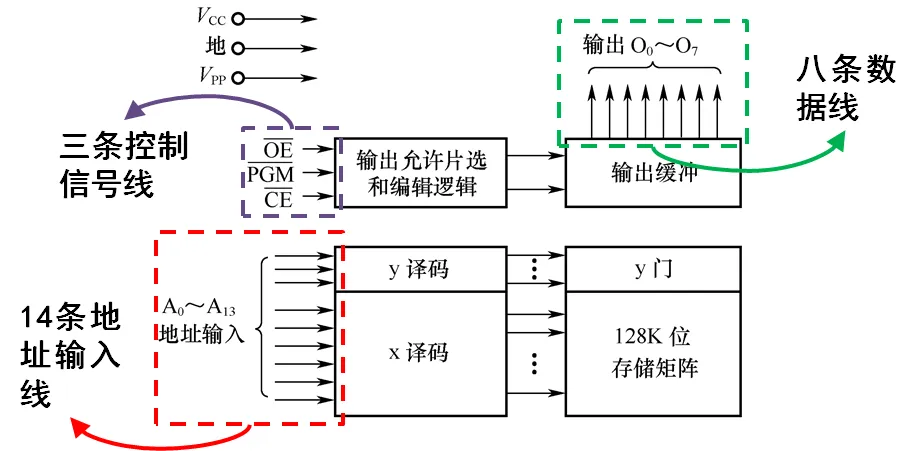

2.4. 高集成度 EPROM (Intel 27128)

- Intel 27128 的最大访问时间为 250ns;

- Intel 27128 是一个128K(16K × 8 位)的 EPROM,需要 14 条地址输入线,经过译码后选中一个单元,此单元的8位同时输出,有8条数据线。

- 输出、编程和各种工作方式由三条控制线:选片信号 、输出允许信号 和编程控制信号 。

Intel 27128 的 8 种工作方式,,

| 方式/引脚 | 输出端 | ||||||

|---|---|---|---|---|---|---|---|

| 读 | 低 | 低 | 高 | × | 数据输出 | ||

| 输出禁止 | 低 | 高 | 高 | × | 高阻 | ||

| 备用 | 高 | × | × | × | 高阻 | ||

| 编程 | 低 | 高 | 低 | × | 数据输入 | ||

| 校验 | 低 | 低 | 高 | × | 数据输出 | ||

| 编程禁止 | 高 | × | × | × | 高阻 | ||

| Intel 标识符 | 低 | 低 | 高 | 高 | 编码 | ||

| Intel 编程方法 | 低 | 高 | 低 | × | 数据输入 |

2.5 例题

在 8086 系统中,用 32K × 8 位的 EPROM 27256 和 2K × 8 位的静态 RAM 6116,构成一个 32KB 的ROM(末端地址 FFFFFH)和 8KB 的 RAM(从 00000H 开始),设 CPU 工作于最小模式。写出 ROM和 RAM 的地址范围。

- 芯片数量:EPROM 27256 1 片,RAM 6116 4片

- 片内地址定义

- EPROM 片内地址:

- RAM 片内地址:

- 译码地址定义

- EPROM 片选地址:=

1111# EPROM CS - RAM 片选地址:

- =

0000 0000 0# CS0 - =

0000 0000 1# CS1 - =

0000 0001 0# CS2 - =

0000 0001 1# CS3

- =

- EPROM 片选地址:=

四. 提高存储器性能的技术

1. Cache

1.1. 映像方式

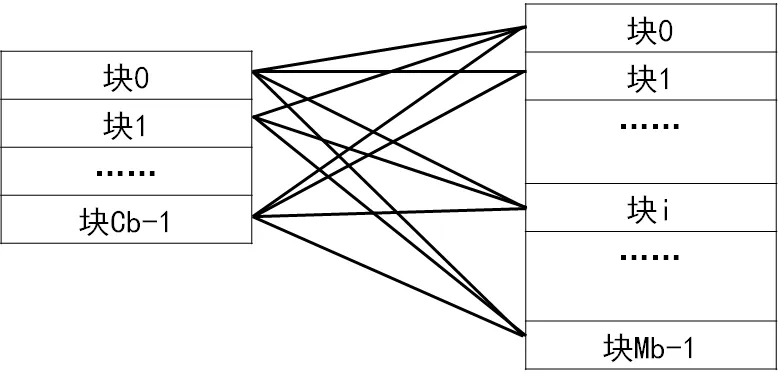

1.1.1. 全相联映像

- 主存与缓存分成相同大小的数据块,主存的任意一块可以映象到 Cache 中的任意一块。

- 全相联映像模式下,命中率较高,Cache 存储空间利用率高,但是,速度低、成本高。

1.1.2. 直接相联映像

- 主存与缓存分成相同大小的数据块,主存容量应是缓存容量的整数倍;

- 将主存空间按缓存的容量分成区,主存中每一区的块数与缓存的总块数相等,主存储器中某区的一块存入缓存时只能映象到 Cache 的一个特定块中。

- 简言之,Cache 块号 = 主存块号 % Cache 块数

- 直接相联映像方式简单,数据访问时只需要检查区号即可,因此可以获得较快的访问速度,硬件设施简单。但替换操作频繁,命中率比较低。

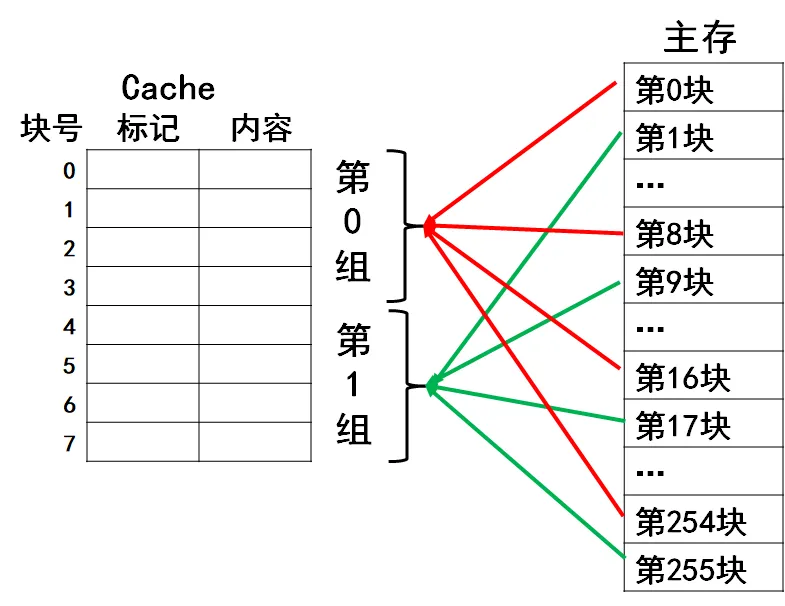

1.1.3. 组相联映像

- 主存和 Cache 分成相同大小的数据块,主存容量应是缓存容量的整数倍,主存按照 Cache 的大小分成区;

- 主存的数据调入缓存时,主存与缓存的组号应相等,组内各块地址之间可以任意存放,即从主存的组到 Cache 的组之间采用直接映象方式;两个对应的组内部采用全相联映象方式。

- 简言之,Cache 组号 = 主存块号 % Cache 组数,每组内有一些小块。

- 组相联映像中块的冲突概率比较低,块的利用率大幅提高。

1.2. 读写过程

CPU 访问主存时首先访问 Cache,在 Cache 中查找所需数据

1.2.1. 读过程

查找和读出可以同时进行,如果找到数据则读出信息正确,如果没有找到读出信息作废则访问主存将对应主存块调入 Cache,再进行读操作

1.2.2. 写过程

查找和读出不能同时进行,只有找到之后才能进行写操作

- 写回法:执行写操作时只写入 Cache,并作标志,替换时才写入主存,这种方式复杂不能保证主存和 Cache 内容一致性,但是速度快;

- 直写法:写入Cache的同时也写入主存,这种方法简单,但是速度慢。

1.3. 替换策略

- 随机法:随机替换存储块;

- 先进先出法:最先调入并被多次命中的块,优先替换;

- 最近最少使用法:最近最少使用的块被替换。

2. 虚拟存储器

由主存和硬盘的一部分构成,在系统软件和辅助硬件的管理下可以当主存使用。虚拟存储器作为一种主存-辅存层次的存储系统,解决了主存容量不足的问题,使得用户可以在一个很大的存储空间编程,不必考虑主存的实际大小。

3. 并行存储器

- 双端口存储器:具有两个彼此独立的读写口,每个读写口都有一套自己的地址寄存器和译码电路,可以并行独立工作;

- 多体并行存储器:由多个独立的,容量相同的存储模块构成,每个模块各自以等同的方式与CPU传递信息,既能并行工作,又能交叉工作。

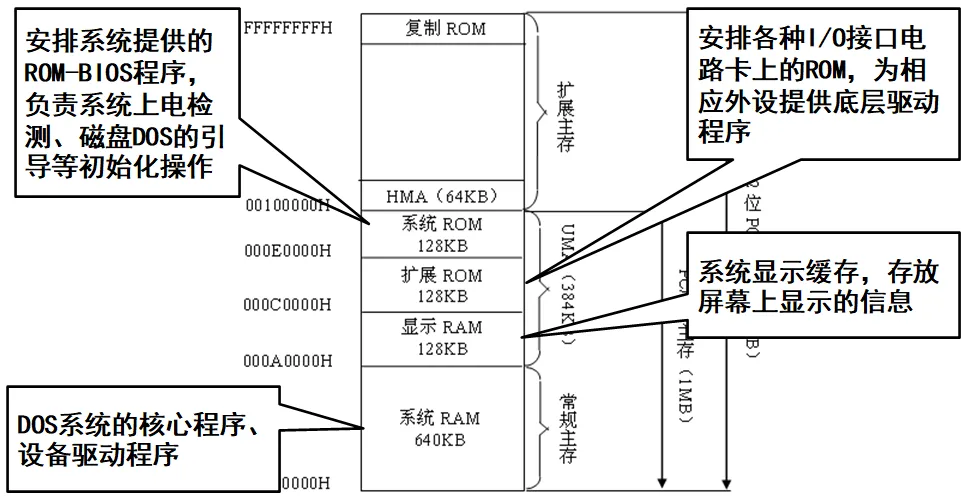

五. 微机主存空间的分配

主存是微处理器能直接存取指令和数据的部分,能否合理地利用主存,很大程度上将影响到整个计算机的性能:

- 系统 RAM 区:DOS 系统的核心程序、设备驱动程序

- 显示 RAM 区:系统显示缓存,存放屏幕上显示的信息

- 扩展 ROM 区:安排各种 I/O 接口电路卡上的 ROM,为相应外设提供底层驱动程序

- 系统 ROM 区:安排系统提供的 ROM-BIOS 程序,负责系统上电检测、磁盘 DOS 的引导等初始化操作